The SPICE Source for: Simulating Hybrid Circuits

of Single-Electron Transistors and Fied Effect Transistors

This file contains links to the source code for the simulations presented in

the article

Simulating Hybrid Circuits of Single-Electron Transistors

and Field-Effect Transistors

Günther Lientschnig, Irek Weymann, and Peter Hadley

Applied Sciences and DIMES, Delft University of Technology

Lorentzweg 1, 2628 CJ Delft, The Netherlands

Japanese Journal of Applied Physics 42 pp. 6467-6472 (2003)

doi: 10.1143/JJAP.42.6467.

In this article, a model for a single-electron transistor (SET) was developed

within the circuit simulation package SPICE. Circuits including single-electron

transistors, field-effect transistors (FET’s), and operational amplifiers

were then simulated.

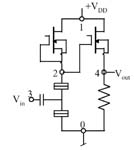

The SPICE model for a SET

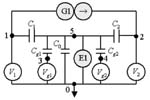

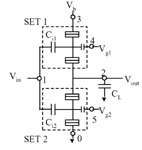

The schematic circuit diagram of the SET SPICE model used for the simulations

in the article is shown below. The source code of the SPICE subsircuit definition

can also be donloaded.

The white voltage sources representing the bias and gate voltages

are external to the SET SPICE model and the gray sources are internal to the

model. E1 is a voltage source that defines the voltage of the island of the

SET (node 5) and G1 is a current source that specifies the source - drain

current from node 1 to node 2.

In the SET SPICE model, the most probable charge state

is calculated first, and then the master equation for the eleven charge states

around this state is solved to calculate the values for E1 and G1.

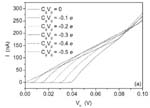

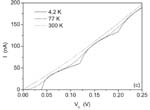

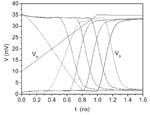

Using this model, the current-voltage charateristics for a SET and the stationary

and transient behavior of circuits containing SET's can be calculated with SPICE.

All simulations presented in the article are listed below. The graphs can be

enlarged by cliking on them, and the SPICE source code can be downloaded. For

more information on the circuits, please refer to the article.

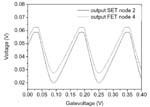

I-V Characteristics of a SET

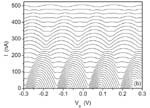

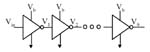

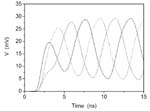

I-V Characteristic and Transient Behavior of a SET Inverter

and a Ring Oscillator

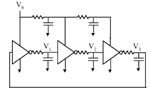

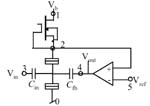

Hybrid Circuits Consisting of SET's and FET's